-

生物通官微

陪你抓住生命科技

跳动的脉搏

集成电路学院黄如院士-叶乐副教授课题组在“超低功耗AIoT芯片”领域取得2项重要研究成果

【字体: 大 中 小 】 时间:2022年04月01日 来源:北京大学新闻网

编辑推荐:

课题组研制并实现了异步脉冲神经网络处理芯片,长时平均功耗为82nW,芯片演示的异常心电识别率为90.5%,此时峰值功耗为350nW,延迟为40微秒;单位脉冲计算能效为0.5pJ/SOP,为当前报道国际同类工作的最好能效水平,与IBMTrueNorthSNN类脑芯片相比,单位脉冲计算能效提高了5倍。

近日,被业界誉为“集成电路国际奥林匹克盛会”的第69届国际固态电路会议(International Solid-State Circuits Conference, ISSCC)采取线上会议形式举办;本届ISSCC大会上,北京大学集成电路学院黄如院士-叶乐副教授课题组的2项“超低功耗智能物联网AIoT芯片”成果,分别收录于前瞻技术(Technology Directions)和存储器(Memory)这两个技术领域,黄如-叶乐课题组已连续三年在ISSCC上发表5项“超低功耗智能物联网AIoT芯片”成果,表明北京大学在该领域已处于国际领先水平。具体介绍如下:

一、“异步脉冲神经网络处理芯片”成果介绍

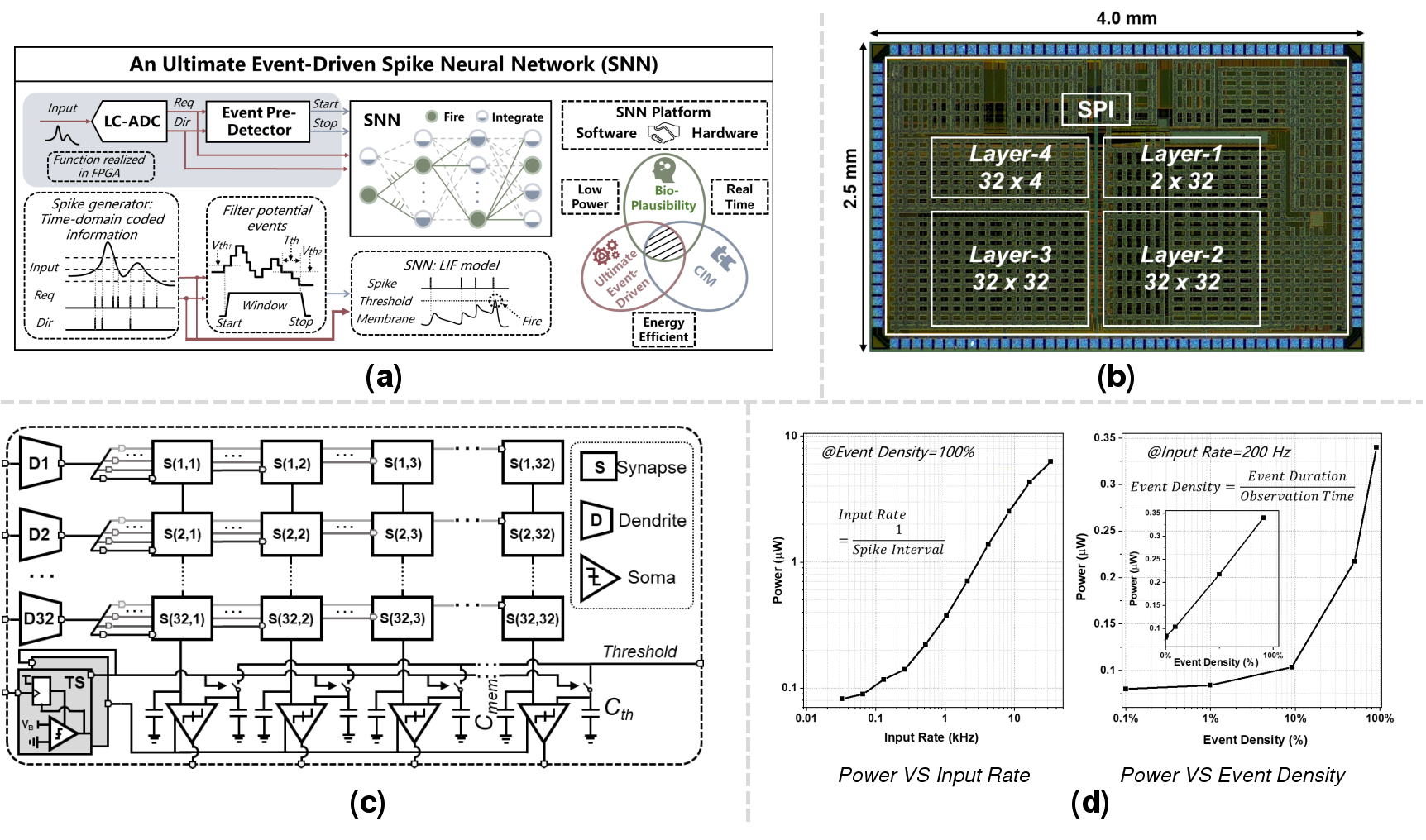

面向智能物联网应用场景,针对同步时钟和存算分离导致AI处理能效低的问题,课题组提出了无时钟异步脉冲神经网络(SNN)架构及电路拓扑,利用具备天然事件触发特性的脉冲神经网络替代传统的人工神经网络,在实现与ANN可比拟推断精度的同时,能够以超低功耗、超低延迟的代价实现轻量级AI推断处理;该创新使得芯片活跃度与外部事件活跃度高度匹配,提升了计算能效;并且去除了同步时钟网络,从而消除芯片待命状态下的主要功耗来源。课题组同时提出了模拟域存算融合的LIF(Leakage-Ingegrate-Fire)神经元电路拓扑,利用LIF神经元的时间信息提取能力,对由事件驱动型传感前端输出的时间编码脉冲序列,实现时间信息提取,降低了AI智能推断过程中所需的运算操作数。此外,还利用存算一体的突触-神经元连接方式,避免了权重数据的频繁搬运,进一步降低了系统功耗。

基于上述创新技术,课题组研制并实现了异步脉冲神经网络处理芯片,长时平均功耗为82nW(on-call waiting for events),芯片演示的异常心电识别率为90.5%,此时峰值功耗为350nW,延迟为40微秒;单位脉冲计算能效为0.5pJ/SOP,为当前报道国际同类工作的最好能效水平,与IBMTrueNorthSNN类脑芯片(2.5pJ/SOP)相比,单位脉冲计算能效提高了5倍。该创新具有高能效、低延时、低功耗等特性,为智能物联网AIoT芯片提供了一种高能效嵌入式AI引擎的重要技术方案,可应用于可穿戴设备、智能语音交互、人体生理信号监测、动态视觉智能识别等物联网应用场景。该创新有望进一步拓展出大规模异步脉冲神经网络芯片。

该工作以《用于AIoT唤醒功能的基于终极事件驱动仿生架构以及存内计算技术的82nW、0.53pJ/SOP以及40微秒推断延迟的无时钟脉冲神经网络芯片》(An 82nW 0.53pJ/SOP Clock-Free Spiking Neural Network with 40μs Latency for AIoT Wake-Up Functions Using Ultimate-Event-Driven Bionic Architecture and Computing-in-Memory Technique)为题,发表于今年ISSCC的前瞻技术领域Session 22(Cryo-Circuits and Ultra-Low Power Intelligent IoT),由文章第一作者北京大学集成电路学院博士生刘影进行宣讲,北京大学集成电路学院博士后王志轩为共同一作。相关研究工作得到了国家重点研发计划、国家自然科学基金等项目的资助,以及浙江省北大信息技术高等研究院、杭州微纳核芯电子科技有限公司等平台的支持。

图1. (a)多层级异步事件触发型AIoT芯片解决方案示意图;(b)异步脉冲神经网络芯片的显微照片;(c)异步脉冲神经网络芯片的架构图;(d)芯片功耗测试波形

二、“超低漏电SRAM存储器芯片”成果介绍

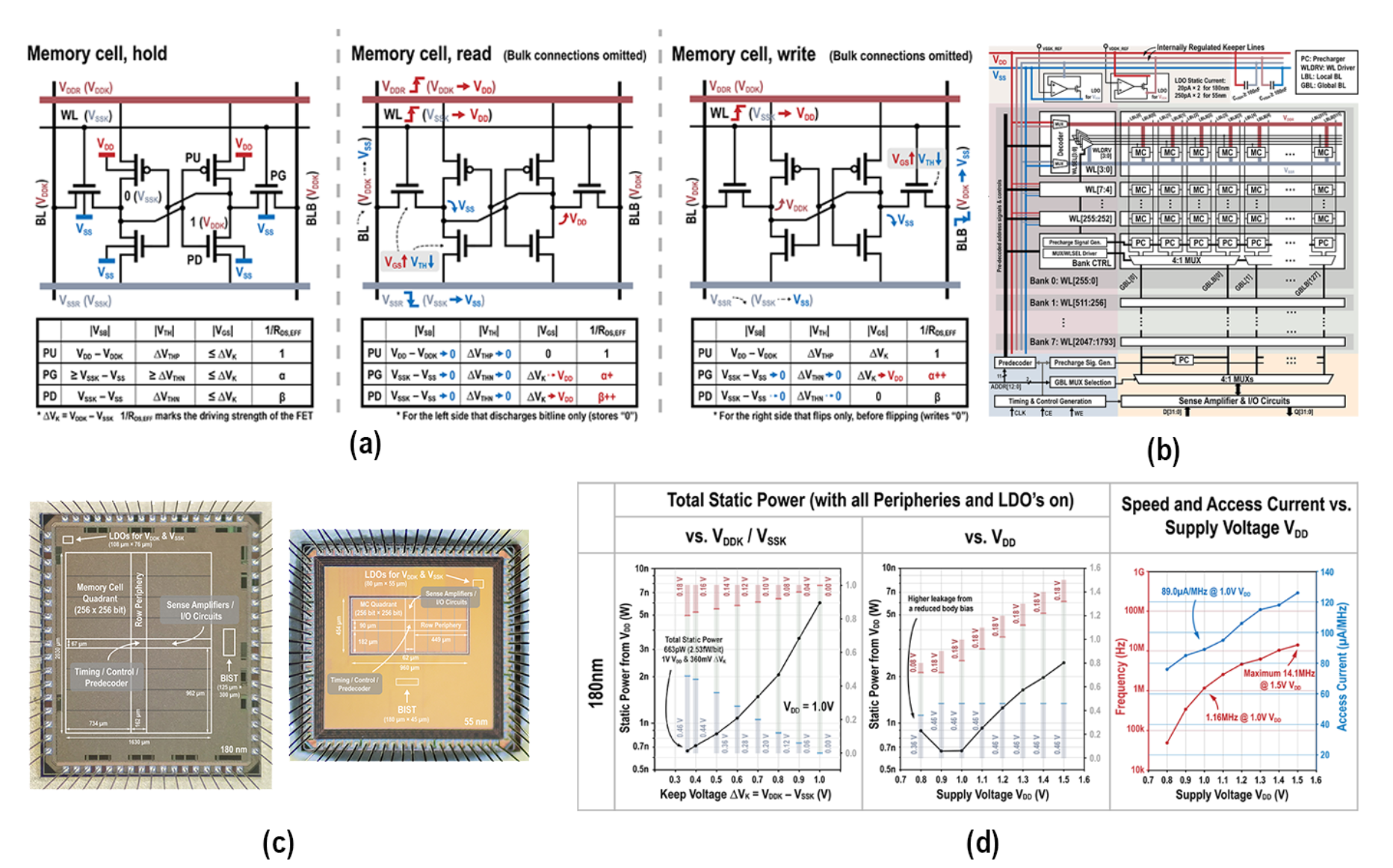

面向智能物联网AIoT芯片应用,针对“实时待命”状态下神经网络权重数据存储的静态漏电问题,提出了超低漏电SRAM存储器架构及电路拓扑,在实现国际最低漏电水平同时,兼顾了高速读写性能。课题组同时提出了基于行/列分布式可变供电技术,解决了传统SRAM频繁模式切换导致延迟与功耗增加的问题,在AIoT芯片随机且稀疏的存储数据访取环境下,进一步降低了功耗。课题组还提出了电压负载免维持技术,消除了动态衬底偏置技术引入的偏置电压保持所需的额外高功耗稳压器,使SRAM在系统级仍可实现超低的静态功耗。

基于上述创新技术,课题组研制并实现了2款不同标准CMOS工艺的超低漏电SRAM存储器芯片。其中,基于180nm标准CMOS工艺实现的256kb SRAM存储器芯片,静态功耗仅为2.5fW/bit,在相同工艺的国际同类工作中实现了最低静态功耗;基于55nm标准CMOS工艺实现的256kb SRAM存储器芯片,静态功耗仅为55fW/bit,在相同工艺的国际同类工作中实现了最低静态功耗。上述2款不同工艺的SRAM存储器芯片,均基于自研的SRAMCompliler生成,可快速应用于多个国产工艺节点。该技术具备超低漏电、高存储密度、高读写速度等特性,可广泛应用于边缘端设备的神经网络权重数据存储和特征数据存储。

该工作以《面向智能物联网平台的基于无保持负载的周边电路与行分离式动态衬底偏置的单一模式2.53fW/bit漏电的6TCMOSSRAM模块》(Single-Mode 6T CMOS SRAM Macros with Keeper-Loading-Free Peripherals and Row-Separate Dynamic Body Bias Achieving 2.53fW/bit Leakage for AIoT Sensing Platforms)为题,发表于今年ISSCC的存储器领域Session 11(Compute-in-Memory and SRAM),由文章第一作者北京大学集成电路学院博士后张奕涵进行宣讲。相关研究工作得到了国家重点研发计划、国家自然科学基金等项目的资助,以及浙江省北大信息技术高等研究院、杭州微纳核心电子科技有限公司等平台的支持。

图2. (a) SRAM单元电路拓扑的示意图;(b) SRAM阵列拓扑的示意图;(c)基于180nm与55nm工艺的256kb SRAM芯片的显微照片;(d)静态功耗、动态功耗、速度的测试结果

ISSCC会议背景介绍:

ISSCC会议每年2月中旬在美国旧金山召开,是国际公认的规模最大、领域内最权威、水平最高的芯片设计领域学术会议,被业界誉为“集成电路设计国际奥林匹克盛会”,每年约有200项芯片实测成果入选,约四成左右的芯片成果来自于国际芯片巨头公司,例如:英特尔、三星、台积电、AMD、英伟达、高通、博通、ADI、TI、联发科等,其余六成左右的芯片成果来自于高校和科研院所;历史上入选ISSCC的成果代表着当年度全球领先水平,展现出芯片技术和产业的发展趋势,多项“芯片领域里程碑式发明”在ISSCC首次披露,如:世界上第一个集成模拟放大器芯片(1968年)、第一个8位微处理器芯片(1974年)和32位微处理器芯片(1981年)、第一个1Gb内存DRAM芯片(1995年)、第一个多核处理器芯片(2005年)等。